Mô hình hóa transistor màng mỏng hữu cơ điện áp thấp trên đế plastic

Điện tử hữu cơ đạt được nhiều thành tựu trong những năm gần đây nhưng việc thiết kế mạch tích hợp hữu cơ vẫn chưa được thực hiện phổ biến với độ chính xác cao vì các linh kiện cơ bản còn chưa có mô hình đặc trưng.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Bạn đang xem tài liệu "Mô hình hóa transistor màng mỏng hữu cơ điện áp thấp trên đế plastic", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Mô hình hóa transistor màng mỏng hữu cơ điện áp thấp trên đế plastic

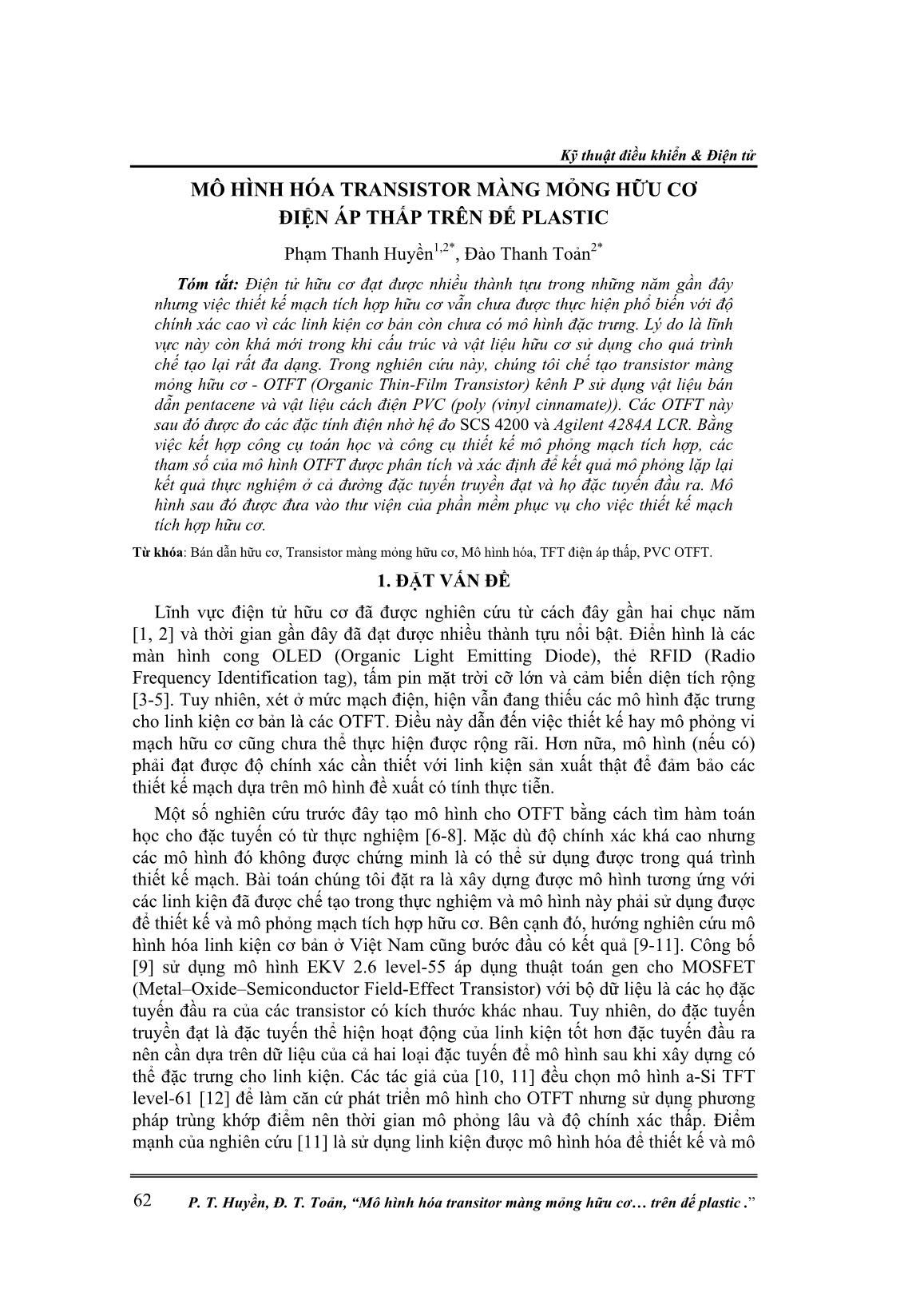

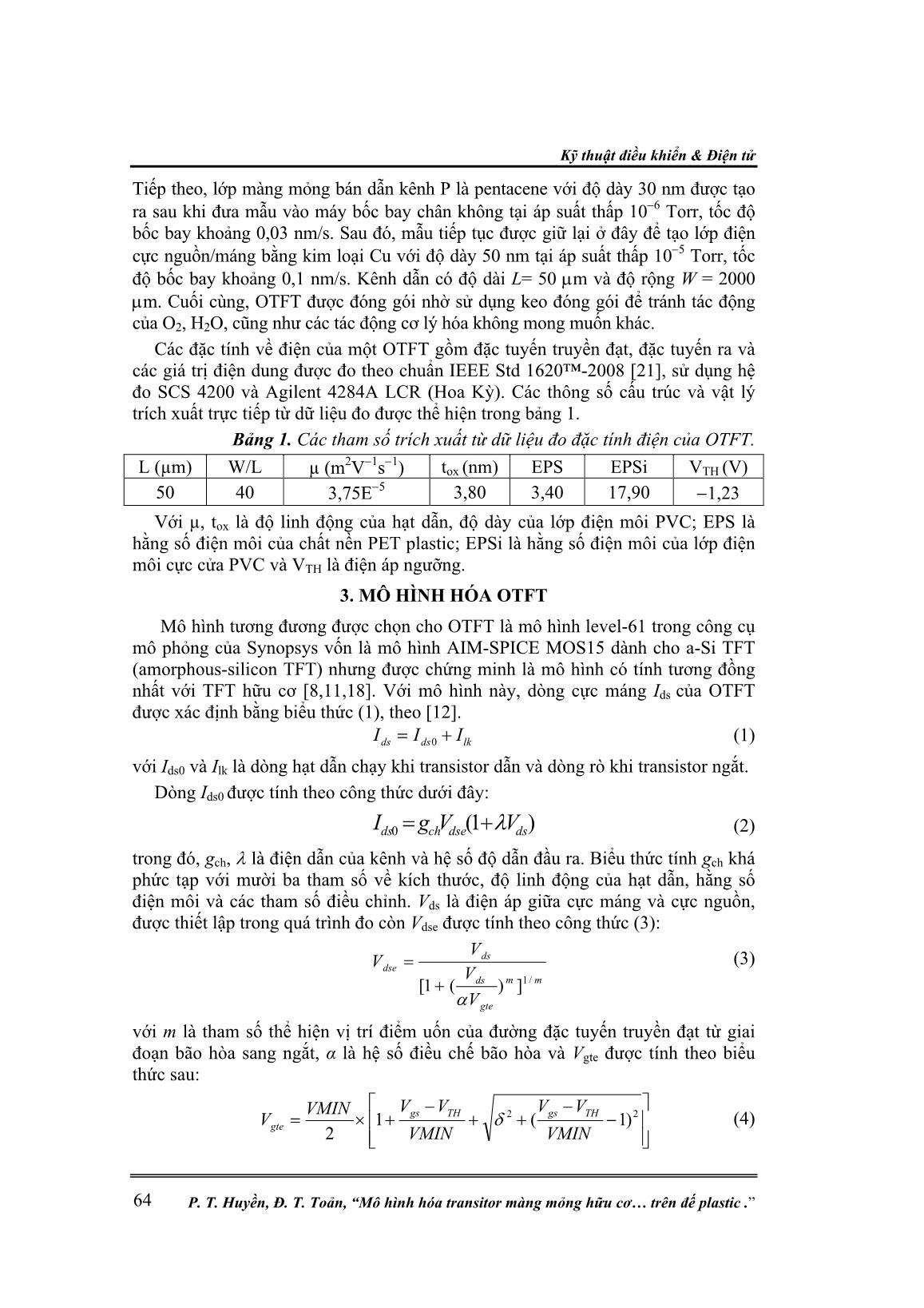

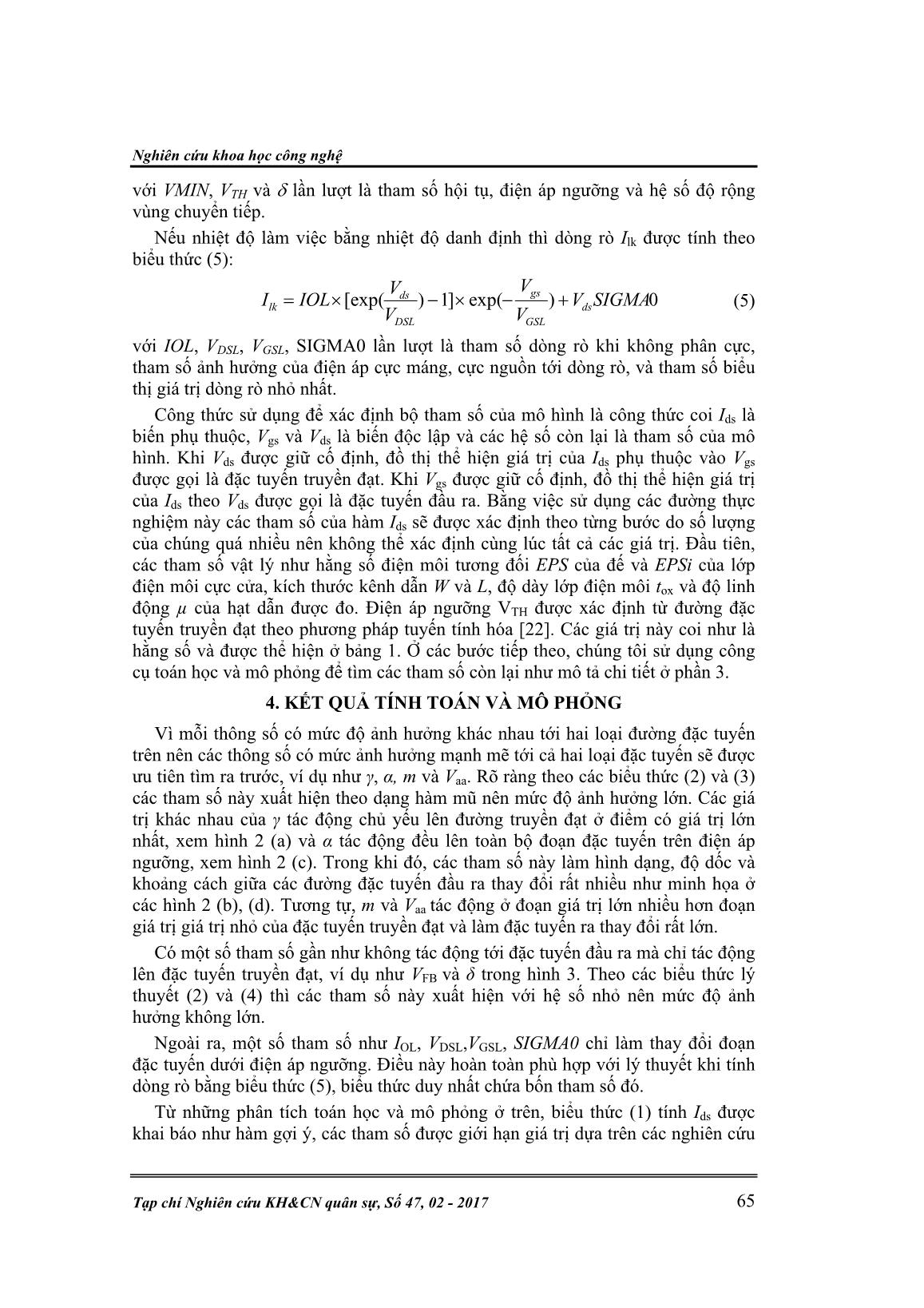

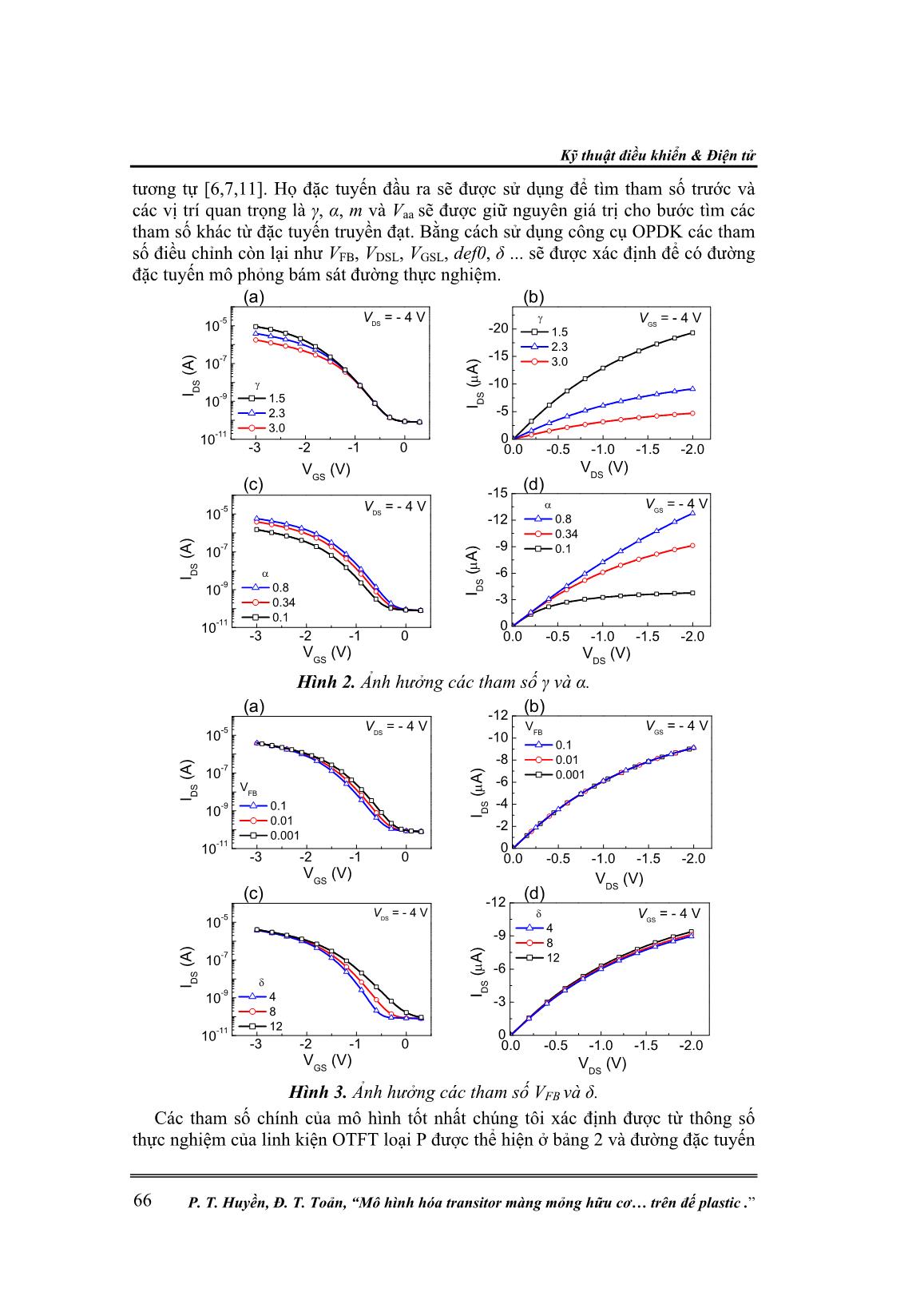

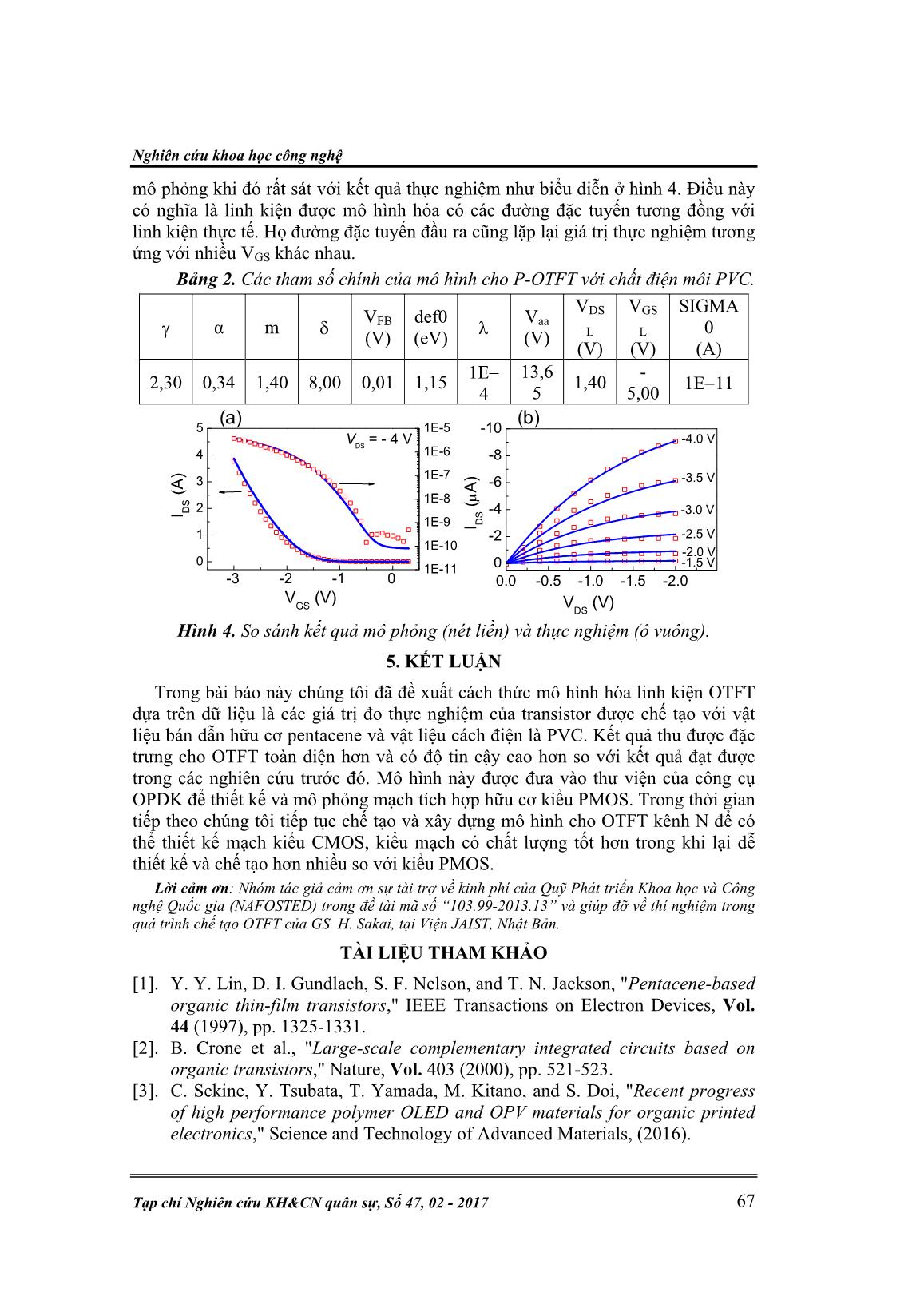

Kỹ thuật điều khiển & Điện tử P. T. Huyền, Đ. T. Toản, “Mô hình hóa transitor màng mỏng hữu cơ trên đế plastic .” 62 MÔ HÌNH HÓA TRANSISTOR MÀNG MỎNG HỮU CƠ ĐIỆN ÁP THẤP TRÊN ĐẾ PLASTIC Phạm Thanh Huyền1,2*, Đào Thanh Toản2* Tóm tắt: Điện tử hữu cơ đạt được nhiều thành tựu trong những năm gần đây nhưng việc thiết kế mạch tích hợp hữu cơ vẫn chưa được thực hiện phổ biến với độ chính xác cao vì các linh kiện cơ bản còn chưa có mô hình đặc trưng. Lý do là lĩnh vực này còn khá mới trong khi cấu trúc và vật liệu hữu cơ sử dụng cho quá trình chế tạo lại rất đa dạng. Trong nghiên cứu này, chúng tôi chế tạo transistor màng mỏng hữu cơ - OTFT (Organic Thin-Film Transistor) kênh P sử dụng vật liệu bán dẫn pentacene và vật liệu cách điện PVC (poly (vinyl cinnamate)). Các OTFT này sau đó được đo các đặc tính điện nhờ hệ đo SCS 4200 và Agilent 4284A LCR. Bằng việc kết hợp công cụ toán học và công cụ thiết kế mô phỏng mạch tích hợp, các tham số của mô hình OTFT được phân tích và xác định để kết quả mô phỏng lặp lại kết quả thực nghiệm ở cả đường đặc tuyến truyền đạt và họ đặc tuyến đầu ra. Mô hình sau đó được đưa vào thư viện của phần mềm phục vụ cho việc thiết kế mạch tích hợp hữu cơ. Từ khóa: Bán dẫn hữu cơ, Transistor màng mỏng hữu cơ, Mô hình hóa, TFT điện áp thấp, PVC OTFT. 1. ĐẶT VẤN ĐỀ Lĩnh vực điện tử hữu cơ đã được nghiên cứu từ cách đây gần hai chục năm [1, 2] và thời gian gần đây đã đạt được nhiều thành tựu nổi bật. Điển hình là các màn hình cong OLED (Organic Light Emitting Diode), thẻ RFID (Radio Frequency Identification tag), tấm pin mặt trời cỡ lớn và cảm biến diện tích rộng [3-5]. Tuy nhiên, xét ở mức mạch điện, hiện vẫn đang thiếu các mô hình đặc trưng cho linh kiện cơ bản là các OTFT. Điều này dẫn đến việc thiết kế hay mô phỏng vi mạch hữu cơ cũng chưa thể thực hiện được rộng rãi. Hơn nữa, mô hình (nếu có) phải đạt được độ chính xác cần thiết với linh kiện sản xuất thật để đảm bảo các thiết kế mạch dựa trên mô hình đề xuất có tính thực tiễn. Một số nghiên cứu trước đây tạo mô hình cho OTFT bằng cách tìm hàm toán học cho đặc tuyến có từ thực nghiệm [6-8]. Mặc dù độ chính xác khá cao nhưng các mô hình đó không được chứng minh là có thể sử dụng được trong quá trình thiết kế mạch. Bài toán chúng tôi đặt ra là xây dựng được mô hình tương ứng với các linh kiện đã được chế tạo trong thực nghiệm và mô hình này phải sử dụng được để thiết kế và mô phỏng mạch tích hợp hữu cơ. Bên cạnh đó, hướng nghiên cứu mô hình hóa linh kiện cơ bản ở Việt Nam cũng bước đầu có kết quả [9-11]. Công bố [9] sử dụng mô hình EKV 2.6 level-55 áp dụng thuật toán gen cho MOSFET (Metal–Oxide–Semiconductor Field-Effect Transistor) với bộ dữ liệu là các họ đặc tuyến đầu ra của các transistor có kích thước khác nhau. Tuy nhiên, do đặc tuyến truyền đạt là đặc tuyến thể hiện hoạt động của linh kiện tốt hơn đặc tuyến đầu ra nên cần dựa trên dữ liệu của cả hai loại đặc tuyến để mô hình sau khi xây dựng có thể đặc trưng cho linh kiện. Các tác giả của [10, 11] đều chọn mô hình a-Si TFT level-61 [12] để làm căn cứ phát triển mô hình cho OTFT nhưng sử dụng phương pháp trùng khớp điểm nên thời gian mô phỏng lâu và độ chính xác thấp. Điểm mạnh của nghiên cứu [11] là sử dụng linh kiện được mô hình hóa để thiết kế và mô Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 47, 02 - 2017 63 phỏng nhiều mạch, trong đó có mạch chuyển đổi tương tự/số phức tạp, tuy nhiên, mô hình mới chỉ áp dụng cho điện áp làm việc cao cỡ hàng chục vôn. Ở khía cạnh khác, để giảm điện áp làm việc của OTFT xuống còn vài vôn có thể thực hiện bằng cách dùng thêm lớp SAM [13,14], Al2O3 [15] hay HfO2 [16] ở lớp điện môi cực cửa. Tuy nhiên, SAM OTFT có dòng dò lớn do hạt dẫn dễ dàng di chuyển qua lớp màng mỏng SAM còn linh kiện Al2O3 và HfO2 lại không phù hợp với sản xuất trên đế dẻo. Thời gian gần đây, PVC được sử dụng như là giải pháp cho OTFT điện áp thấp trên đế dẻo [17,18] nhưng mô hình của loại OTFT này hiện vẫn chưa có nghiên cứu nào đề cập tới. Trong bài báo này, chúng tôi kết hợp cả phân tích đặc tính về điện của PVC OTFT điện áp thấp, công cụ toán học OriginPro và công cụ mô phỏng OPDK (Organic Process Design Kit) để tìm ra bộ tham số của mô hình. OriginPro là công cụ hỗ trợ xử lý dữ liệu và đồ thị còn OPDK là công cụ thiết kế mạch tích hợp hữu cơ [19]. Với phương pháp tiếp cận mới này của chúng tôi, quá trình mô phỏng được thực hiện nhanh hơn và kết quả thể hiện đặc tính của OTFT toàn diện hơn. Thêm nữa, mô hình được phát triển trên nền tảng từ chương trình thiết kế mạch tích hợp nên hoàn toàn có thể sử dụng cho quá trình thiết kế và mô phỏng mạch. 2. CHẾ TẠO OTFT KÊNH P VỚI CHẤT ĐIỆN MÔI PVC Chúng tôi sử dụng kiến trúc “cực cửa bên dưới, cực nguồn và máng bên trên” (bottom-gate top-contact) vì khi này điện cực nguồn/máng sẽ được lắng đọng bên trên lớp bán dẫn, làm cho phần tiếp xúc hiệu dụng giữa điện cực và bán dẫn lớn hơn các kiểu cấu trúc khác, qua đó làm giảm điện trở tiếp xúc của điện cực và bán dẫn [20]. Điện cực cửa G LW G S/DS/D Đóng gói Điện môi PVC PVC Pentacence Tấm nền plastic Mẫu sau khi sản xuất Hình 1. Mô tả quá trình sản xuất OTFT kênh P trên tấm nền plastic. Quá trình sản xuất được mô tả ở hình 1. Tấm nền plastic được rửa bằng dung dịch trong phòng sạch và làm khô để đảm bảo loại bỏ O2 và H2O trên bề mặt. Sau đó, tấm nền được đưa vào máy bốc bay chân không với áp suất thấp 10 5 Torr và tốc độ bốc bay khoảng 0,3 nm/s để tạo lớp điện cực cửa bằng Al với độ dày là 30 nm. Lớp màng mỏng điện môi PVC có độ dày khoảng 34 nm được tạo ra bên trên điện cực cửa bằng phương pháp quay phủ sau khi polyme PVC được hòa tan vào dung dịch DMF (dimethyl formamide) với tỉ lệ 5 mg/ml. Để giảm dòng rò, tia cực tím UV được chiếu khoảng 1 giờ vào mẫu trên nhằm gia cố liên kết bên trong lớp điện môi. Kỹ thuật điều khiển & Điện tử P. T. Huyền, Đ. T. Toản, “Mô hình hóa transitor ... ng số cấu trúc và vật lý trích xuất trực tiếp từ dữ liệu đo được thể hiện trong bảng 1. Bảng 1. Các tham số trích xuất từ dữ liệu đo đặc tính điện của OTFT. L (µm) W/L µ (m2V 1s 1) tox (nm) EPS EPSi VTH (V) 50 40 3,75E 5 3,80 3,40 17,90 1,23 Với µ, tox là độ linh động của hạt dẫn, độ dày của lớp điện môi PVC; EPS là hằng số điện môi của chất nền PET plastic; EPSi là hằng số điện môi của lớp điện môi cực cửa PVC và VTH là điện áp ngưỡng. 3. MÔ HÌNH HÓA OTFT Mô hình tương đương được chọn cho OTFT là mô hình level-61 trong công cụ mô phỏng của Synopsys vốn là mô hình AIM-SPICE MOS15 dành cho a-Si TFT (amorphous-silicon TFT) nhưng được chứng minh là mô hình có tính tương đồng nhất với TFT hữu cơ [8,11,18]. Với mô hình này, dòng cực máng Ids của OTFT được xác định bằng biểu thức (1), theo [12]. lkdsds III 0 (1) với Ids0 và Ilk là dòng hạt dẫn chạy khi transistor dẫn và dòng rò khi transistor ngắt. Dòng Ids0 được tính theo công thức dưới đây: )1(0 dsdsechds VVgI (2) trong đó, gch, là điện dẫn của kênh và hệ số độ dẫn đầu ra. Biểu thức tính gch khá phức tạp với mười ba tham số về kích thước, độ linh động của hạt dẫn, hằng số điện môi và các tham số điều chỉnh. Vds là điện áp giữa cực máng và cực nguồn, được thiết lập trong quá trình đo còn Vdse được tính theo công thức (3): mm gte ds ds dse V V V V /1])(1[ (3) với m là tham số thể hiện vị trí điểm uốn của đường đặc tuyến truyền đạt từ giai đoạn bão hòa sang ngắt, α là hệ số điều chế bão hòa và Vgte được tính theo biểu thức sau: 22 )1(1 2 VMIN VV VMIN VVVMIN V THgsTHgsgte (4) Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 47, 02 - 2017 65 với VMIN, VTH và lần lượt là tham số hội tụ, điện áp ngưỡng và hệ số độ rộng vùng chuyển tiếp. Nếu nhiệt độ làm việc bằng nhiệt độ danh định thì dòng rò Ilk được tính theo biểu thức (5): 0)exp(]1)[exp( SIGMAV V V V V IOLI ds GSL gs DSL ds lk (5) với IOL, VDSL, VGSL, SIGMA0 lần lượt là tham số dòng rò khi không phân cực, tham số ảnh hưởng của điện áp cực máng, cực nguồn tới dòng rò, và tham số biểu thị giá trị dòng rò nhỏ nhất. Công thức sử dụng để xác định bộ tham số của mô hình là công thức coi Ids là biến phụ thuộc, Vgs và Vds là biến độc lập và các hệ số còn lại là tham số của mô hình. Khi Vds được giữ cố định, đồ thị thể hiện giá trị của Ids phụ thuộc vào Vgs được gọi là đặc tuyến truyền đạt. Khi Vgs được giữ cố định, đồ thị thể hiện giá trị của Ids theo Vds được gọi là đặc tuyến đầu ra. Bằng việc sử dụng các đường thực nghiệm này các tham số của hàm Ids sẽ được xác định theo từng bước do số lượng của chúng quá nhiều nên không thể xác định cùng lúc tất cả các giá trị. Đầu tiên, các tham số vật lý như hằng số điện môi tương đối EPS của đế và EPSi của lớp điện môi cực cửa, kích thước kênh dẫn W và L, độ dày lớp điện môi tox và độ linh động µ của hạt dẫn được đo. Điện áp ngưỡng VTH được xác định từ đường đặc tuyến truyền đạt theo phương pháp tuyến tính hóa [22]. Các giá trị này coi như là hằng số và được thể hiện ở bảng 1. Ở các bước tiếp theo, chúng tôi sử dụng công cụ toán học và mô phỏng để tìm các tham số còn lại như mô tả chi tiết ở phần 3. 4. KẾT QUẢ TÍNH TOÁN VÀ MÔ PHỎNG Vì mỗi thông số có mức độ ảnh hưởng khác nhau tới hai loại đường đặc tuyến trên nên các thông số có mức ảnh hưởng mạnh mẽ tới cả hai loại đặc tuyến sẽ được ưu tiên tìm ra trước, ví dụ như γ, α, m và Vaa. Rõ ràng theo các biểu thức (2) và (3) các tham số này xuất hiện theo dạng hàm mũ nên mức độ ảnh hưởng lớn. Các giá trị khác nhau của γ tác động chủ yếu lên đường truyền đạt ở điểm có giá trị lớn nhất, xem hình 2 (a) và α tác động đều lên toàn bộ đoạn đặc tuyến trên điện áp ngưỡng, xem hình 2 (c). Trong khi đó, các tham số này làm hình dạng, độ dốc và khoảng cách giữa các đường đặc tuyến đầu ra thay đổi rất nhiều như minh họa ở các hình 2 (b), (d). Tương tự, m và Vaa tác động ở đoạn giá trị lớn nhiều hơn đoạn giá trị giá trị nhỏ của đặc tuyến truyền đạt và làm đặc tuyến ra thay đổi rất lớn. Có một số tham số gần như không tác động tới đặc tuyến đầu ra mà chỉ tác động lên đặc tuyến truyền đạt, ví dụ như VFB và δ trong hình 3. Theo các biểu thức lý thuyết (2) và (4) thì các tham số này xuất hiện với hệ số nhỏ nên mức độ ảnh hưởng không lớn. Ngoài ra, một số tham số như IOL, VDSL,VGSL, SIGMA0 chỉ làm thay đổi đoạn đặc tuyến dưới điện áp ngưỡng. Điều này hoàn toàn phù hợp với lý thuyết khi tính dòng rò bằng biểu thức (5), biểu thức duy nhất chứa bốn tham số đó. Từ những phân tích toán học và mô phỏng ở trên, biểu thức (1) tính Ids được khai báo như hàm gợi ý, các tham số được giới hạn giá trị dựa trên các nghiên cứu Kỹ thuật điều khiển & Điện tử P. T. Huyền, Đ. T. Toản, “Mô hình hóa transitor màng mỏng hữu cơ trên đế plastic .” 66 tương tự [6,7,11]. Họ đặc tuyến đầu ra sẽ được sử dụng để tìm tham số trước và các vị trí quan trọng là γ, α, m và Vaa sẽ được giữ nguyên giá trị cho bước tìm các tham số khác từ đặc tuyến truyền đạt. Bằng cách sử dụng công cụ OPDK các tham số điều chỉnh còn lại như VFB, VDSL, VGSL, def0, δ ... sẽ được xác định để có đường đặc tuyến mô phỏng bám sát đường thực nghiệm. 0.0 -0.5 -1.0 -1.5 -2.0 0 -5 -10 -15 -20 V GS = - 4 V I D S ( A ) V DS (V) 1.5 2.3 3.0 -3 -2 -1 0 10 -11 10 -9 10 -7 10 -5 1.5 2.3 3.0 V GS (V) V DS = - 4 V I D S ( A ) -3 -2 -1 0 10 -11 10 -9 10 -7 10 -5 0.8 0.34 0.1 V GS (V) V DS = - 4 V I D S ( A ) 0.0 -0.5 -1.0 -1.5 -2.0 0 -3 -6 -9 -12 -15 V GS = - 4 V I D S ( A ) V DS (V) 0.8 0.34 0.1 (a) (b) (c) (d) Hình 2. Ảnh hưởng các tham số γ và α. 0.0 -0.5 -1.0 -1.5 -2.0 0 -2 -4 -6 -8 -10 -12 V GS = - 4 V I D S ( A ) V DS (V) V FB 0.1 0.01 0.001 (a) (b) -3 -2 -1 0 10 -11 10 -9 10 -7 10 -5 V FB 0.1 0.01 0.001 V GS (V) V DS = - 4 V I D S ( A ) -3 -2 -1 0 10 -11 10 -9 10 -7 10 -5 4 8 12 V GS (V) V DS = - 4 V I D S ( A ) 0.0 -0.5 -1.0 -1.5 -2.0 0 -3 -6 -9 -12 V GS = - 4 V I D S ( A ) V DS (V) 4 8 12 (c) (d) Hình 3. Ảnh hưởng các tham số VFB và δ. Các tham số chính của mô hình tốt nhất chúng tôi xác định được từ thông số thực nghiệm của linh kiện OTFT loại P được thể hiện ở bảng 2 và đường đặc tuyến Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 47, 02 - 2017 67 mô phỏng khi đó rất sát với kết quả thực nghiệm như biểu diễn ở hình 4. Điều này có nghĩa là linh kiện được mô hình hóa có các đường đặc tuyến tương đồng với linh kiện thực tế. Họ đường đặc tuyến đầu ra cũng lặp lại giá trị thực nghiệm tương ứng với nhiều VGS khác nhau. Bảng 2. Các tham số chính của mô hình cho P-OTFT với chất điện môi PVC. α m VFB (V) def0 (eV) Vaa (V) VDS L (V) VGS L (V) SIGMA 0 (A) 2,30 0,34 1,40 8,00 0,01 1,15 1E 4 13,6 5 1,40 - 5,00 1E 11 1E-11 1E-10 1E-9 1E-8 1E-7 1E-6 1E-5 -3 -2 -1 0 0 1 2 3 4 5 V DS = - 4 V I D S ( A ) V GS (V) 0.0 -0.5 -1.0 -1.5 -2.0 0 -2 -4 -6 -8 -10 -1.5 V -2.0 V -2.5 V -3.0 V -3.5 V -4.0 V I D S ( A ) V DS (V) (a) (b) Hình 4. So sánh kết quả mô phỏng (nét liền) và thực nghiệm (ô vuông). 5. KẾT LUẬN Trong bài báo này chúng tôi đã đề xuất cách thức mô hình hóa linh kiện OTFT dựa trên dữ liệu là các giá trị đo thực nghiệm của transistor được chế tạo với vật liệu bán dẫn hữu cơ pentacene và vật liệu cách điện là PVC. Kết quả thu được đặc trưng cho OTFT toàn diện hơn và có độ tin cậy cao hơn so với kết quả đạt được trong các nghiên cứu trước đó. Mô hình này được đưa vào thư viện của công cụ OPDK để thiết kế và mô phỏng mạch tích hợp hữu cơ kiểu PMOS. Trong thời gian tiếp theo chúng tôi tiếp tục chế tạo và xây dựng mô hình cho OTFT kênh N để có thể thiết kế mạch kiểu CMOS, kiểu mạch có chất lượng tốt hơn trong khi lại dễ thiết kế và chế tạo hơn nhiều so với kiểu PMOS. Lời cảm ơn: Nhóm tác giả cảm ơn sự tài trợ về kinh phí của Quỹ Phát triển Khoa học và Công nghệ Quốc gia (NAFOSTED) trong đề tài mã số “103.99-2013.13” và giúp đỡ về thí nghiệm trong quá trình chế tạo OTFT của GS. H. Sakai, tại Viện JAIST, Nhật Bản. TÀI LIỆU THAM KHẢO [1]. Y. Y. Lin, D. I. Gundlach, S. F. Nelson, and T. N. Jackson, "Pentacene-based organic thin-film transistors," IEEE Transactions on Electron Devices, Vol. 44 (1997), pp. 1325-1331. [2]. B. Crone et al., "Large-scale complementary integrated circuits based on organic transistors," Nature, Vol. 403 (2000), pp. 521-523. [3]. C. Sekine, Y. Tsubata, T. Yamada, M. Kitano, and S. Doi, "Recent progress of high performance polymer OLED and OPV materials for organic printed electronics," Science and Technology of Advanced Materials, (2016). Kỹ thuật điều khiển & Điện tử P. T. Huyền, Đ. T. Toản, “Mô hình hóa transitor màng mỏng hữu cơ trên đế plastic .” 68 [4]. T. Sekitani and T. Someya, "Stretchable organic integrated circuits for large- area electronic skin surfaces," MRS Bulletin, Vol. 37, No. 03 (2012), pp. 236-245. [5]. OE-A, “OE-A Roadmap for Organic and Printed Electronics,” (2016). [6]. O. Marinov, M. J. Deen, U. Zschieschang, and H. Klauk, "Organic thin-film transistors: Part I—Compact DC modeling," IEEE Transactions on Electron Devices, Vol. 56 (2009), pp. 2952-2961. [7]. M. Estrada et al., "Accurate modeling and parameter extraction method for organic TFTs," Solid-state electronics, Vol. 49 (2005), pp. 1009-1016. [8]. C. Kim, Y. Bonnassieux, and G. Horowitz, "Compact DC modeling of organic field-effect transistors: Review and perspectives," IEEE Transactions on Electron Devices, Vol. 61 (2014), pp. 278-287. [9]. L. D. Hung, N. D. N. Tam, B. T. Tu, "Parameter Extraction for EKV 2.6 MOSFET Model Based on Genetic Algorithm", Journal of Science and Technology, Vietnam Academy of Science and Technology, Vol. 52 (2014), pp. 46-56. [10]. T. T Ho, H. T. Pham, H. Sakai, T. T. Dao, "Fabrication and SPICE Modeling of a Low-voltage Organic Thin-film Transistor with PVC gate dielectric", Proc. of 3rd International Conference on Advanced Materials and Nanotechnology (ICAMN), Hanoi (2016), pp. 308-311. [11]. H. T. Pham, T. V. Nguyen, L. Pham-Nguyen, H. Sakai, and T. T. Dao, "Design and Simulation of a 6-Bit Successive-Approximation ADC Using Modeled Organic Thin-Film Transistors," Active and Passive Electronic Components, Vol. 2016, (2016). [12]. Synopsys, "HSPICE - Reference Manual: MOSFET Models," Synopsys, Technical report (2012). [13]. K. Kuribara et al., "Organic transistors with high thermal stability for medical applications," Nature Communications, Vol. 3 (2013), pp.723. [14]. P. Wobkenberg et al., "Low-voltage organic transistor based on solution processed semiconductos and self-assemble monolayer gate dielectrics," Applied Physics Letter, Vol. 93 (2008), pp. 13303. [15]. S. Kim et al., "Ink-jet-printed organic thin-film transistors for low-voltage- driven CMOS circuits with solution-processed AlOx gate insulator," IEEE Electron Device Letter, Vol. 34 (2013), pp.307–309. [16]. X. -H. Zhang, S. P. Tiwari, S.-J. Kim, and B. Kippelen, "Low-voltage pentacene organic field-effect transistors with high-K HfO2 gate dielectrics and high stability under bias stress," Applied Physics Letter, Vol. 95 (2009), pp. 223302. [17]. L. Feng et al., "Unencapsulated air-stable organic field effect transistor by all solution processes for low power vapor sensing," Science Report, Vol.6 (2016), pp. 20671. [18]. L. Feng, W. Tang, X. Xu, Q. Cui, and X. Guo, "Ultralow-voltage solution- processed organic transistors with small gate dielectric capacitance," IEEE Electron Device Letters, Vol. 34 (2013) , 129-131. [19]. University of Minnesota VLSI Group, “The Organic Process Design Kit” Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 47, 02 - 2017 69 (OPDK). [20]. I.Kymissis, “Organic Field Effect Transistors: Theory, Fabrication and Characterization,” Springer, New York (2008). [21]. IEEE, "IEEE Standard for Test Methods for the Characterization of Organic Transistors and Materials - Redline," IEEE Std. 1620-2008 (Revision of IEEE Std. 1620-2004) - Redline, (2008), pp. 1-27. [22]. F. Yakuphanoglu, S. Mansouri, and R. Bourguiga, "Extracting parameters from current--voltage characteristics of pentacene field-effect transistor in saturation region," Synthetic Metals, Vol. 162 (2012), pp. 918-923. ABSTRACT MODELlNG OF LOW-VOLTAGE ORGANIC THIN-FILM TRANSISTOR ON PLASTIC SUBSTRATE Organic electronics has reached many achievements recently; However, processes of design and simulation integrated circuits have not been implemented precisely because of lacking of models for basic elements. In this work, P-channel organic thin-film transistors (OTFT) are fabricated with pentacene as organic semiconductor, and PVC (poly (vinyl cinnamate)) as gate dielectric. Physical specifications and electrical characteristics of the OTFTs are measured with SCS 4200 and Agilent 4288A LCR systems. Parameters of the model are extracted by analyzing theory and using simulation tools. The results prove that our model replicates the experimental data of both the transfer and output characteristics. Then the modeled device is added in simulation tools to design integrated circuits. Keywords: Organic semiconductor, Organic thin-film transistor, Modeling, Low-voltage, PVC OTFT. Nhận bài ngày 07 tháng 12 năm 2016 Hoàn thiện ngày 29 tháng 01 năm 2017 Chấp nhận đăng ngày 20 tháng 02 năm 2017 Địa chỉ: 1Viện Điện tử - Viễn Thông, Trường Đại học Bách Khoa Hà Nội; 2Khoa Điện-Điện tử, Trường Đại học Giao thông Vận tải; * Email: huyenktdt@utc.edu.vn; daotoan@utc.edu.vn.

File đính kèm:

mo_hinh_hoa_transistor_mang_mong_huu_co_dien_ap_thap_tren_de.pdf

mo_hinh_hoa_transistor_mang_mong_huu_co_dien_ap_thap_tren_de.pdf